# Performance Analysis of FIR Filter design for Secure Applications-A Review

<sup>1</sup>Mohana Kannan Loganathan, <sup>2</sup>Deepa.D <sup>1</sup>Research scholar, Anna university, Chennai.Tamil Nadu <sup>2</sup>Professor, Bannari Amman institute of technology, Sathyamangalam, Tamil Nadu

#### Abstract

In this research, recent advances in low power architectures and algorithms are analysed based on the Finite Impulse filter (FIR) design. Filter designs are applied in several applications like medical diagnosing, image/Speech processing and arithmetic computations. In various applications, a FIR is a channel whose impulse response is of limited period, because of it settles to zero in finite time. The filtering operations are executed continuously or in discrete manner. The major challenges of FIR filters are simultaneous approximationin both magnitude and phase responses. Likewise, the designer faces lot of issues while constructing the alternative trade-offs. The filter design must provide goodefficiency and simplicity. Hence, this research reviewed the recent filtering application based articles to extract the exact problem in designing the FIR filter realization. In low power aspects, the delay and power are the two major attributes that affect the overall performance of the filter applications. This work considers several motivation and suggestions carried out by existing researches and it is come into view as a crucial area in integration devices. There is a huge number of filtering designs have been associated with respect to the implementations. This researchcoined out the key ideas to examine various schemes in filtering applications along with its solutions.

Keywords--- Finite Impulse filter, Digital filter design, Evolutionary algorithms, Digital signal processing.

### I. Introduction

The advanced digital frameworks are upgraded with the most fundamental zone of VLSI configuration [1]. In recent days, a significant scope of research work completed in advancing successful models to minimize the sophistication of DSP framework. The most essential part of the Digital Signal Processing (DSP) system contains this FIR filter operations particularly for arithmetic operation [2]. It contributes morearithmetic and logical operations for estimating the signal and equalization process. It utilize more calculations for generating the filter coefficients. In most of the cases, the critical path delay of filter decides the speed of the whole applications, due to the internal addition and multiplication process. The contribution of the multiplier and adder are the key equipment pieces of FIR channel to decrease the chip region, power and delay for each iteration.

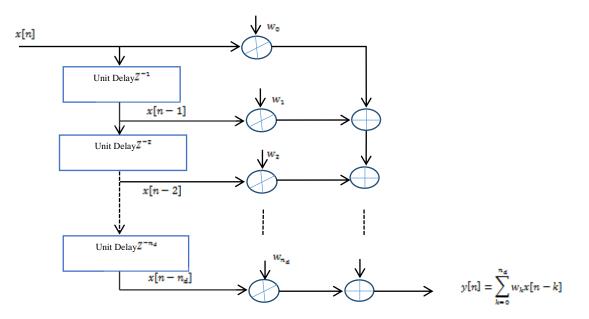

As shown in the figure 1, the "tap" is one of the delay pair, the total number of taps are denoted by 'N'. The performance and characteristics of FIR filter contains the filter coefficients such as constants, tap weights or delay values. The impulse response is one of the important process that is proceeded by a unityvalued sample with respect to the zero-valued samples. For an FIR filter the impulse response of a FIR filter is the set of filter coefficients. The response is denoted as H(z) or h(n) which determines the filter operations that follows the Kronecker delta function. If the number of taps gets increases then the complexity also gets increases. The major aspect is the total amount of memory needed, computations and the amount of "filtering" needed. If the number of taps gets increased then the filter results in better stop band attenuation and provides less rippling and steeper roll off.

Digital signal processing calculations are progressively utilized in present day remote interchanges and interactive media in customer service, for example, cell phones and computerized cameras. The new age of media advancement frequently requires the utilization of low-power FIR filters. The normal filtering operation results in elimination of noise and remove unwanted signals. The efficient way of filtering operation is defined by the power, delay and area of the internal computation units. The process will be formulated by reviewing the complexities present in the FIR filter design. The major drawbacks are identified in traditional algorithmic methods are premature convergence and unacceptable computational cost. In some cases, the hybrid schemes are used to merge the features from one algorithm and integrate it with another phenomenon. The normal filter design deals with the transfer function of a circuit or a program. The common methods of filter design is window technique, frequency sampling and optimization.

International Journal of Advanced Information in Engineering Technology (IJAIET) Vol.5, No.3, March 2018

Figure 1: The 'n' Stage FIR filter design

The necessity of filter design is described as follows:

- 1. The need for FIR filter design is optimize the complex problem.

- 2. The designed filter module must satisfy the highly nonlinear and multimodal concepts.

- 3. The selected algorithm must be fast and efficient for processing all the local solutions

- 4. The filter must provide better solutions with the help of nearest local optima value.

- 5. In complex multimodal problem, the solution must be focused on exact initialization point with respect to the output attributes.

Most of the FIR filter design consists of two essential problems like approximation and realization problem. In the approximation type, the ideal response is selected with the ideal response which is in terms of the frequency domain. The quality of measure is selected to find the best transfer function. Similarly, the realization part deals with the structure of circuit by means of windows method, frequency sampling or by the optimal filter design modules.

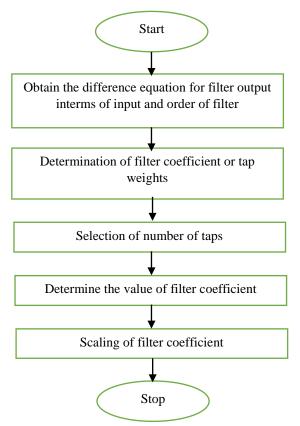

The complexity of FIR filters used in various signal processing blocks is conquered by the quantity of adders or sub tractors employed in the multipliers. The alternative method to replace the traditional method is software defined radio (SDR) technology. It is an innovative technique that replaces transmitters and receivers that offering a wide range of merits including adaptability, reconfigurability and multi-functionality.Research in this field is fundamentally coordinated towards enhancing the engineering and the computational effectiveness of SDR frameworks. The most computationally concentrated piece of a SDR unit is the channelizer since it works at the most sampling rate. The general algorithmic format for FIR filter design is shown in the figure 2.

The major effects of windowing technique in terms of frequency response is described below:

- i. A real impact is that discontinuities in H (w) progress toward band values on either side of the discontinuity.

- ii. The width of the transition bands relies upon the width of the principle flap of the frequency reponse of the window task, w (n)

- Since the channel recurrence frequency is acquired by means of a convolution, obviously the subsequent channels are never ideal in any sense.

- iv. As length of the window work expands, the principle flap width of (w) is decreased. It lessens the width of the progress band, however this additionally presents more ripple in the frequency reaction.

- v. The window function wipes out the ringing impacts at the band edge and results in lower side flaps to the detriment of an expansion in the width of the progress band of the channel. Therefore the h(n) can got for the desired estimation of cut off recurrence.

The major objective of designing the digital filter is to process the input discrete time signal and result same type of output signal by matching the filtering process [3]. A sample flow chart is shown in the figure 2. The performance of the digital filter is directly depends upon the discrete values which are stored in the registers, that may vary easily. The importance of selecting FIR filter instead of Infinite Impulse Response (IIR) filters because of its linearphase property stability and it is low sensitivity to coefficient. The normal transition width of a FIR filter is inversely proportional to the filter length. In rare cases, the high order filters create more problem while implementing. The arithmetic applications normally suggest FIR filter to because it requires less power when comparing it with the IIR filter. The high speed and low power also achieved in FIR when comparing it with the IIR.

Figure 1.2 Flow chart for FIR filter design

The essentialactions in FIR filter involves multiplication and repeated accumulation of filter coefficients with the input digital data. It is completely processed by the adders and multipliers. In VLSI signal processing, the multiplier and adders are the two major power consuming blocks. Hence, the researchers focussed on multiplier less FIR filter design. Hence, the traditional multipliers are completely replaced with shift and adder circuits. In such cases, the constants are represented as sums or differences of signed-power-of-two terms (SPT). The adder cost depends on the number of SPT terms present in the filter coefficients, hence the reduction in complexity of FIR filters. This research has been examined and focussed on the essential of filter design in all types of applications. The remaining of this work is organized as follows: section II describes about the conventional methodologies with a detail survey with its technique and usage. It also identified the problem and declared the drawbacks. Finally, the article is summarized in section III.

#### II. Literature survey

Mohanty and Meher (2013) presented an efficient Distributed Arithmetic (DA) operation for implementing the Block Least Mean Square (BLMS) algorithm. It is mainly designed with the utilization of Look-Up Table (LUT)-sharing concept for computing the respective filter outputs. When comparing with the various Adaptive Digital Filter (ADF), least mean square (LMS)-based FIR adaptive filter is results in compact design and different performance satisfaction. Since, the feedback error occurrence of the weights are planned to upgrade the weights and it never support the pipeline processes. It is completely processed and designed with the block-size 8 and filter length 64. The implementation proves that the adaptive filter may process even in high computations with minimum ADP and Energy per sample.

Mohanty et al., (2014) analysed the memory and the investigation of conceivable storage enhancement to have a memory-proficient outline methodology for the execution of 2-D FIR channel. Shared memory plan for divisible and non-distinguishable structures. Planning of computations and engineering outline for memoryreuse and memory band-width diminishment in detachable filters. Unified structure of channel bank included detachable and non-distinguishable channels with low memory impression per single fan out. The completely coordinate non-distinct structure and also the regular detachable structure utilize shift registers to store 'M' words each, however shift registers of completely coordinate non-distinct structure stores input pixel esteems while those of divisible structure stores middle of the road esteems. Because of the distinction in bitwidth, a typical transfer enlist unit can't be shared by these two structures. It investigated the novel block based divisible and non-distinguishable structures, nonspecific structures for distinct and non-detachable channel banks and bound together structure for simultaneous acknowledgment of both distinct and non-detachable channel banks. It is demonstrated that capacity prerequisite of proposed structures does not change with input square size L.

In recent years, the role of evolutionary algorithms are considered to design the filter with various filter length, pass band and stop band frequencies. Ababneh and Bataineh (2008) proposed a linear phase FIR filter which is framed with the help of Particle Swarm Optimization (PSO) and Genetic Algorithms (GA). The filter design is framed with the filter coefficients under finite word length sequence. It also selected the explicit selection of swarm in filtering concepts. With a simple nature, a linear phase Low pass Filter (LPF) is presumed here to test both GA and PSO concepts in filtering process. The process is simplified because of the PSO algorithm format, parameter selection format, filter coefficients and so on. Finally, PSO results in better convergence when comparing it with the traditional GA fitness value.

Kotha et al., (2014)stated that the Differential evolution (DE) is applied for FIR filter design to optimize the parameter and improve the quality of the design. The parameters like signedpower-of-two and the frequency response of filter design is optimized. Apart from different attributes, the DE is merged with the following attributes Strategy (S), Mutant factor (F) and Cross-over probability (Cr). The FIR filter must contain an extensive number of channel coefficients equivalent to 0, with the end goal that circuit parts comparing to zero-esteemed coefficients are never again required. Inadequate FIR channels can be utilized as a part of different applications.

The traditional sparse FIR channels are composed as channel shortening equalizers, where a SNR expansion issue is illuminated with respect to a lostandard imperative or constraint. Hence, Jiang et al., (2012) framed a sparse FIR filter design that concentrate on the issue of recurrence specific FIR channels. It should be noticed that each channel coefficient is thought to be genuine esteemed and can be improved s per methodology. In this manner, the inadequate FIR channel plan under thought is basically a ceaseless enhancement problem, which varies from the ones managing discrete channel coefficients. Further, the Jiang and Kwan (2013) extended their research to reduce the delay that occurring in nonzero-valued filter. In 2014, the filter design is extended to optimize the problem with the help of Iterative-Reweighted-Least-Squares (IRLS).

The linear phase Multiply–accumulate operation is developed to maintain the filter design. The process of merging the partial product generation and the propagation unit takes more time to deliver the result. Due to this delay, the computation complexity is arises. It is completely based on the booth encoding process carried out by Rashidi et al., (2011). The booth encoder is constructed by merging the X-OR operation, buffer and Multiplexer units. It supports linear phase FIR filter designs with huge number of transformations. It is tested with different transformations on 6 tap, 10 tap and 13 tap Filter combinations in Virtex II processer with the MATLAB. It is represented with the help of data transition power diminution technique combined with booth and replacing with AND gate.

In most of the cases, the adder and multiplier results in complex design. Hence, there is a need for reducing the internal computational units. Hence, Tsao et al., (2011) presented a 3parallel 576-tap filter with the reduction of 192 multipliers and seven adders. It is designed particularly for symmetric convolutions applications. Tsao et al., (2012a) implemented the parallel FIR architectures to perform the high speed operations and it further reduces the multiplier to the half extent. Fast FIR algorithms are discussed here to manage the filter design process. It is designed and tested with different filter tapings namely 27, 81, 147 and 591. The requirement of multiplier is increases with respect to the tap size but still the adder remains constant. Another concept which is developed by Tsao et al., (2012b) is exchanging multipliers with adders. It helps to find out the exact scenario of the FIR filter designs.

Kar et al., (2012) identified the suboptimality problem that are occurring during the implementation of classical optimization methods. Hence, the local minima problem is to be identified and rectified to design exact filtering operation. It avoids the premature convergence and stagnation problem that happens in PSO filtering. Hence, the process of PSO is modified in the craziness format to the diversity of the particles. The process of maintaining the probability of the diversity a new variable is initiated. It is verified with the GA, conventional PSO, Comprehensive Learning PSO (CLPSO) and Parks and McClellan (PM) Algorithm. Finally, the process is summarized that the craziness based PSO is the best one among others. The major limitations of VLSI design is computational cost. It is determined by several optimization techniques to modify the current systems and provide the exact requirement of advancement.

Rani and Sidhu, (2015) also utilized the craziness based PSO for digital band stop FIR design. It provides velocity vector and swarm updating feature to improve the quality. Its performance is compared with the traditional PSO based filter design. It also reduces the magnitude errors and ripple magnitudes of both pass band and stop band. Zhao et al., (2013)presented the formulation of two stage genetic algorithm. It is completely designed with the more zero-valued coefficients. Zhao et al., (2015) compared the

performance of unbiased FIR, minimum variance unbiased FIR, and optimal FIR filters.

researchers applied Many the computational algorithm in FIR algorithms. Likewise, Saha et al., (2013)applied the Cat Swarm Optimization (CSO) in the field of filtering process. It is completely depends upon the cats behaviour, tracking and similar other fitness values. It is compared with the Real Coded Genetic Algorithm, DE and PSO process. The design complexity and the delay is one of the existing problem in all types of filter design. The major outcome of the filter design follows the genetic algorithm, the fitness value provides the exact potential to all complex problems. It is utilized in severalprocess of controlling high voltage devices problems. Hence, the recent algorithm called as CSO is utilized by search agent's iteration.

Mandal et al., (2014) presents a new way of designing linear phase FIR low pass and high pass filter using a bybrid model that combines the Adaptive Differential Evolution (ADE) and PSO. It is selected because it provides simple steps and robust in nature. The filtering operation provides high magnitude as well as convergence speed. The initialization depends upon the search space and the position of the fitness value. Identified the maximum iteration or minimum iteration to process the fitness function. Then, the velocity and the position of the particle is calculated with the help of DE algorithm. After completing the fitness value, the crossover rate is processed with the parent node. Based on the respective iteration, the filtering operation is performed.

Park and Meher (2014) proposed an efficient DA-based concepts for achieving highthroughput reconfigurable implementation of FIR filter. In most of the cases, the filter coefficients are varied based on the variation in time. Normally, the applications are varied with respect to the real time environment and also depends upon the requirement. The changes in the iteration provides enormous problems in designing. The process of combining two different algorithm with unique feature gives the new design. Likewise, the DA based implementation is processed with the help of Look Up table module. The research focused on partial inner products and minimized the complexity. The process is implemented in the Xilinx Virtex-5 FPGA device. Swathi and Revathy (2014) represented the Multi-Standard Digital Up Converter (DUC) with the filter design. The process is carried out with the weight updating block and the shift add block. The delayed least mean square filter is modified with the shift block with the low path delay and power consumption. The Reconfigurable Root-Raised-Cosine process is tested in the Xilinx tool and it is verified by the Field-programmable gate array (FPGA) module.

Ahmad et al., (2014) proposed a most efficient VLSI design for LS cross section for FIR filter. The calculation utilized here is Givens Rotation wherein the computational many-sided quality is decreased from  $O(M^2)$  to simply O(M). This calculation tries to adjust a low power interface on itself and involves a littler surface square unit of region for its VLSI execution. At first the equipment engineering for the blunder refreshing RLS criticism calculation and the coefficient execution units is portrayed. Besides, one such design for Givens RLS cross section stepping stool organize and is processor cluster rationale is depicted. This whole portrayal is actualized on Virtex-5 FPGA (XUPV5LX110T) utilizing VHDL. This usage accomplished the best outcomes for which it possessed just 1075 cut registers, 876 LUT's(1%) giving the extraordinary throughput execution on the outline. The execution influences utilization of roundabout cushions to refresh the Dual Port Memory. This demonstrated a 68.75% expansion in the execution when contrasted with a typical productive VLSI plan.

Chandra et al., (2014) designed a multiplier-less FIR filter design by Self-organizing Random Immigrants Genetic Algorithm (SORIGA). The filter design depends upon the parameter selectionindividual coefficient of an optimization. It is encoded with the sum of signed powers-of-two. The research focused particularly on cross over probability and the frequency response. It suggested to implement this algorithm in various applications and find the best outcome. Further, Chandra and Chattopadhyay (2016) extended the research by analysing the different recent concepts.

Tseng and Lee (2014) displayed the outlines of partial subordinate compelled in a single dimensional (1-D) and different dimensional FIR channels. The derivative of 1-D FIR channels with complex-esteemed recurrence reactions are composed by limiting the vital squares blunder or greatest supreme mistake under the imperative that the real reaction and perfect reaction have a few same fragmentary subsidiaries at the endorsed recurrence point. The strategy is stretched out to outline partial subordinate obliged 2-D FIR channels with complex-esteemed recurrence reactions. It approved to demonstrate that the strategy has bigger outline adaptability than the customary whole number subsidiary compelled techniques.

Nagahara and Yamamoto (2014) proposed a FIR digital filter design that provides enamours approximation in the analog filter for minimizing the H<sup> $\infty$ </sup> norm of the sampled-data error system. It utilizes lifting technique and the Kalman YakubovichPopov (KYP) lemma to minimize the H $\infty$  optimization. It performs the discretization and the extension of the previous process. It suggested to utilize multiplier less FIR filter design to achieve the excellent performance. Punitha and Ramesh (2015) analysed different algorithms that are used in FIR filter design concepts. It is classified in to different types namely, Systolization, symmetry, Diagonal symmetry, and Fourfold Rotational Symmetry.

Kaur et al., (2015) applied a greedy search algorithm for designinginfinite impulse response filter. It optimizes the magnitude and phase response simultaneously with the lowest order of the filter. The process is controlled by the gene along with the filter coefficients. It concentrated more on stability constraints and the trade-off. Hatai et al., (2015) reduces the multiplication units per input sample. Reddy and Sahoo(2015) proposed a hardware efficient FIR filter design using DE and common sub expression elimination algorithm. The process starts with the implementation of filtercoefficients and finally determined the hardware cost.

Raj and Vigneswaran (2016) identified the precision errors and determined the modified FIR filter design with the help of distributed arithmetic (DA). Pak et al., (2016) presented the extensible FIR filter bank (SEFFB) algorithm to reduce the estimation errors. In 2017, they further extended this research with a new nonlinear state estimator with a FIR structure. The process helps to estimate the Extended Least Square Unbiased FIR filter (ELSUFF). The main merit of selecting this issue is that it does not require noise information. The noise are in ambiguous state and deliver exact performance. The traditional filters like Kalman filter and the particle filter provides degrades the performance against the noise model.

The conventional methods are improved to achieve the low power consumption by means of reducing the ripples in pass band and stop band. Hence, Dwivedi et al., (2016) presented an optimization based on the minimization of ripples. These objectives are framed with various concepts by avoiding the ripples present in the filter design. It is fully described with the multi objective optimization process named as artificial bee colony algorithm. It minimizes the designer's complexity and avoid ripples when comparing it with the traditional methods. The process of comparing filter design is varied with respect to the FPGA utilization.

Aggarwal et al., (2016) researched various evolutionary streams by solving the complex

problems in filter design. The process of utilizing the evolutionary algorithm is because of solving the complex problems with various solutions. Various researchers focused on this topic because of its The swarm intelligence nature. based methodologies are flexible and it is best suite for complex problems. The comparison of different SI algorithms are carried out with the cuckoo-search algorithm (CSA), PSO and real-coded genetic algorithm (RCGA). The filter design is carried out with the individual methodologies and functions. It proves that the CSA results in best solution in various aspects. The design error is minimized similar to the execution time.

Kuyu and Vatansever (2016) framed an online or offline based system that is optimized by the filter co-efficient. Before entering in to the evaluation, nine evolutionary algorithms are compared here to facilitate the error functions and tests. It is termed as excellent decision making system and it can be used as per the filter design requirements. It is further tested with the different types of error functions namely, LMS, MAE. Minimax and final ranks of MSE with an average design time. It is tested with the different coefficients and different types of error functions. It is designed to simplify the process of filter.

The traditional Distributed arithmetic (DA) areachieved to plan bit-level architectures for vector-vector multiplication. It is processed directly with an application of convolution, which is necessary for digital filters. The conventional arithmetic operations helps to maintain the single cycle per bit of resolution regardless of filter length is used. Mankar et al., (2016) concentrated more on low power adaptive filter designs by replacing theconditional signed carry-save accumulation instead of conventional adder based shift accumulation so that reduction of the sampling period and area complexity is easy. The major limitations of the DA filters are it requires more modification in calculating the lookup table. It is further implemented in Xilinx ISE 9.1 using Verilog HDL.

Illa et al., (2016) designed the modification of the Johansson and Eghbali (2012) methodology. The impulse response consists of bandwidth and fractional delay parameters. The normal linear phase structure is modified with the pre-designed farrow structure. The utilization of the farrow structures provides a simple nature and variable multiplier up gradation. Dash et al., (2017) framed the Linear Phase Multiband Stop Filter (LPMBSFs) named as a robust hybrid metaheuristic algorithm called improved cuckoo search particle swarm optimization (ICSPSO). Here, the response of the search is identified by the ICSPSO process. It pointed out that the traditional window method and the frequency sampling

methods have no precise control over the stop band and pass band cut-off frequencies.

| S.No | Author                            | Technique and its Usage                                                                                                                                        | Findings                                                                                                                           |

|------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Ababneh and<br>Bataineh<br>(2008) | Linear phase FIR filter design using<br>particle swarm optimization and genetic<br>algorithms                                                                  | Further need to implement it in real<br>time applications and verify                                                               |

| 2    | Rashidi et al.,<br>(2011)         | It concentrated more on reducing the<br>dynamic power consumption in FIR filter<br>design. It is framed byserial multiplier and<br>serial adder.               | It is analysed with only 8bits inputs.<br>Further need to extend input<br>combination and verify                                   |

| 3    | Jiang et al.,<br>(2012)           | Iterative Second Order<br>Cone Programming (SOCP) with iterative<br>shrinkage/ Thresholding technique is<br>proposed                                           | Increase in number of zero-valued coefficients                                                                                     |

| 4    | Tsao and<br>Choi (2012a)          | Exchanging multipliers with adders for providing the excellent parallel FIR filter                                                                             | Implement it in complex algorithm to verify the computation complexity                                                             |

| 5    | Tsao and<br>Choi (2012b)          | Fast finite-impulse response (FIR)<br>algorithms                                                                                                               | The number of multipliers increases if the FIR coefficients varies                                                                 |

| 6    | Kar et al.,<br>(2012)             | Craziness based Particle Swarm<br>Optimization is proposed for filtering<br>operation                                                                          | Computationally<br>Costlier                                                                                                        |

| 7    | Jiang and<br>Kwan (2013)          | Sparse finite impulse response (FIR) is<br>designed to reduce the number of nonzero-<br>valued filter                                                          | It identifies and solve each sub-<br>problem that may results in complex<br>delay                                                  |

| 8    | Mohanty and<br>Meher<br>(2013)    | Parallel architecture is designed for<br>implementing the BLMS adaptive digital<br>filter. It reduces the area delay product and<br>maintain the compatibility | Energy per sample and ADP is high for large filter lengths                                                                         |

| 9    | Zhao et al.,<br>(2013)            | Sparse FIR design with Genetic algorithm                                                                                                                       | Related and slightly modified with the Iterative SOCP.                                                                             |

| 10   | Saha et al.,<br>(2013)            | CSO algorithm is applied for multi-modal optimal FIR filter design problems.                                                                                   | The execution time is to be minimized                                                                                              |

| 11   | Mandal et al.,<br>(2014)          | Framed a combination of Adaptive<br>Differential Evolution (ADE) and Particle<br>Swarm Optimization (PSO)                                                      | Convergence speed must be improved                                                                                                 |

| 12   | Park and<br>Meher<br>(2014)       | Discussed about the DA-based systolic<br>structure and carry save adder (CSA)-<br>based structure.                                                             | The proposed structure has less area as<br>well as shorter minimum sample period<br>compared to the DA-based systolic<br>structure |

| 13   | Jiang et al.,<br>(2014)           | Iterative Reweighted-Least-Squares<br>(IRLS)                                                                                                                   | Based on the filter order the sparsity is determined                                                                               |

| 14   | Swathi and<br>Revathy<br>(2014)   | Multi-Standard DUC Based FIR Filter. It is designed with the help of look up tables                                                                            | Huge delay                                                                                                                         |

| 15   | Mohanty et al., (2014)            | Two-dimensional (2-D) FIR filter design<br>with generic structures for separable and<br>non-separable filter-banks                                             | Need to utilize this process with several filtering applications                                                                   |

## Table 1: Usage and Drawbacks of various techniques

| 16 | Ahmad<br>(2014)                    | RLS lattice ladder FIR filter algorithms using circular buffer technique                                                                                                                                          | Throughput is to be improved                                                                                                              |

|----|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 17 | Chandra et<br>al., (2014)          | Self-organizing Random Immigrants<br>Genetic algorithm (SORIGA)                                                                                                                                                   | The power of the two FIR filter are<br>estimated with the evolutionary<br>calculations. Still the hardware cost<br>will be increased      |

| 18 | Tseng and<br>Lee (2014)            | Fractional derivative constrained one-<br>dimensional (1-D) and two-dimensional<br>(2-D) FIR filters are derived                                                                                                  | It has larger design flexibility                                                                                                          |

| 19 | Nagahara and<br>Yamamoto<br>(2014) | FIR Digital Filter Design by Sampled-<br>Data <sup>*</sup> <i>H</i> <sup>∞</sup> Discretization                                                                                                                   | Not suitable for multi-rate and multi-<br>delay systems                                                                                   |

| 20 | Zhao et al.,<br>(2015)             | The Minimum Variance Unbiased (MVU)<br>FIR filtering problem is analysed for linear<br>system                                                                                                                     | Its iterative realization must be studied<br>to find out the effectiveness                                                                |

| 21 | Punitha and<br>Ramesh<br>(2015)    | Efficient 2-D Finite Impulse<br>Response (FIR) Filter is designed                                                                                                                                                 | Combinational complexity                                                                                                                  |

| 22 | Rani and<br>Sidhu, (2015)          | Craziness Based<br>Particle Swarm Optimization                                                                                                                                                                    | The analysis is carried out in terms of<br>magnitude. Hence, further it may<br>concentrate with other attributes like<br>delay and power. |

| 23 | Kaur et al.,<br>(2015)             | Binary Successive Approximation based digital IIR filter is designed                                                                                                                                              | Its results proved that the proposed<br>method is better than the Evolutionary<br>algorithm                                               |

| 24 | Hatai et al.,<br>(2015)            | Binary common sub-expression is utilized<br>on Reconfigurable Pulse-Shaping FIR<br>Interpolation                                                                                                                  | Further need to reduce area and power                                                                                                     |

| 25 | Reddy and<br>Sahoo<br>(2015)       | Differential Evolution (DE) and Common<br>Sub Expression (CSE) elimination<br>algorithm are utilized                                                                                                              | More delay and power                                                                                                                      |

| 26 | Raj and<br>Vigneswaran<br>(2016)   | Pipeline based DA architecture                                                                                                                                                                                    | Effective reduction of delay as 3.547<br>and memory size is reduced. Further,<br>the memory size need to be reduced.                      |

| 27 | Pak et al.,<br>(2016)              | Switching extensible FIR filter<br>bank (SEFFB) algorithm is proposed and<br>estimation errors are reduced                                                                                                        | Need to improve this algorithm by<br>adapting the horizon size for FIR<br>filtering                                                       |

| 28 | Dwivedi et<br>al., (2016)          | A modified version of multi-objective<br>artificial bee colony algorithm is utilized<br>for designing the FIR filter                                                                                              | Power consumption is reduced, still may get minimized                                                                                     |

| 30 | Aggarwal et<br>al., (2016)         | A digital FIR High Pass and Band Stop<br>filter is designed with the cuckoo search,<br>particle swarm and real-coded genetic<br>algorithm                                                                         | Convergence rate and design accuracy are achieved greatly.                                                                                |

| 31 | Kuyu and<br>Vatansever<br>(2016).  | Genetic Algorithm (GA), Differential<br>Evolution Algorithm (DE), Particle Swarm<br>Optimization algorithm (PSO), Artificial<br>Bee Colony algorithm (ABC), Ant Colony<br>Optimization algorithm (ACO), Simulated | Error functions are analysed with different filtering operations                                                                          |

|    |                                         | Annealing algorithm (SA), firefly<br>Algorithm (FF), Cuckoo Search algorithm<br>(CS) and Harmony Search algorithm (HS)                           |                                                                                                              |

|----|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 32 | Mankar et al.,<br>(2016)                | Distributed arithmetic based Digital FIR<br>Filter is design with the help of LMS<br>Adaptive Algorithm                                          | The power and voltages are to be reduced                                                                     |

| 33 | Chandra and<br>Chattopadhya<br>y (2016) | A hardware efficient FIR filter is designed                                                                                                      | Suggested to implement the FIR filter<br>in communication and signal<br>processing                           |

| 34 | Illa et al.,<br>(2016)                  | Artificial Bee Colony (ABC) optimization is deployed with FIR filter design                                                                      | Performance degradation is to be reduced                                                                     |

| 35 | Mohanty et al., (2016)                  | The realization of block FIR filter in transpose form configuration                                                                              | Area-delay product is reduced.                                                                               |

| 36 | Pak et al.,<br>(2017)                   | Extended least square unbiased FIR filter                                                                                                        | The utilization of the Kalman filter is<br>to be merged with another and improve<br>the filtering operation  |

| 37 | Dash et al.,<br>(2017)                  | Multipurpose digital FIR linear phase<br>double-band filter (LPDBF) design with<br>the Hybrid Firefly Differential Evolution<br>(HFDE) algorithm | The global searching capability helps<br>to solve the problems, but still there is<br>a need for improvement |

| 38 | Liu and Parhi<br>(2017)                 | Linear-phase FIR digital filters using stochastic computing                                                                                      | Signal-to-error ratio is improper                                                                            |

| 39 | Liang and<br>Kwan (2017)                | Multi-objective Cuckoo Search Algorithm<br>(MOCSA)                                                                                               | Filter coefficients are limited. Need to analyse it with different inputs                                    |

| 40 | Raju and<br>Kwan (2017)                 | Multi-objective Artificial Bee Colony<br>algorithm                                                                                               | Magnitude and group delay errors are optimized.                                                              |

Liu and Parhi (2017) presents a new novel architectures for linear phase FIR digital filters using stochastic computing. It requires a fewer logic gates and are inherently fault-tolerant. It is analysed and compared with the direct-form linearphase FIR filters. It minimizes the hardware complexity of the adder and multiplier. The signal to noise ratio is measured with the ICA '99 Synthetic Benchmarks. Liang and Kwan (2017) presented the multi-objective Cuckoo Search Algorithm to reduce magnitude error. Raju and Kwan (2017) combined the Spherical pruning (SP) and physical programming to provide the multi objective PSO. The optimal filter parameters are optimized with the Pareto front.

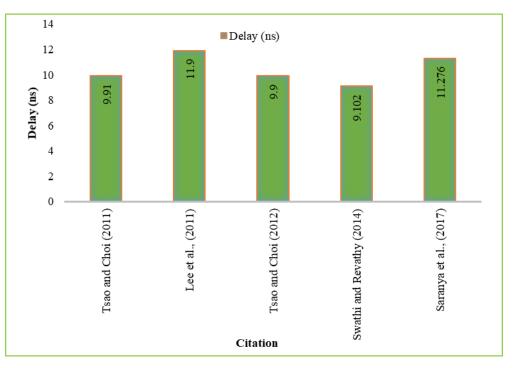

Figure 3 demonstrated that the delay analysis parameter considered from 2011 to 2017 for designing the FIR filter design. In this survey, it is noticed that the delay from Swathi and Revathy (2014) has the least delay. This analysis is carried out for estimating the overall delay. The delay will be varied based on the hardware utilized and the synthesis procedure. Apart from these cases, the technology file is one of the major part in observing the FIR filter design. International Journal of Advanced Information in Engineering Technology (IJAIET) Vol.5, No.3, March 2018

Figure 3: Comparative analysis in terms of Delay

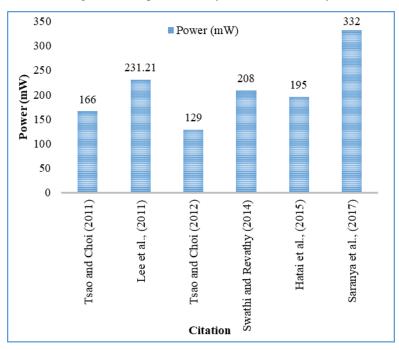

Figure 4: Comparative analysis in terms of Power

Figure 3 demonstrates the power analysis of each and every design process varies with respect to the device. The limited number of research tabulated the power consumption in terms of the power report.

In recent days, the FIR digital filter has received significant consideration from specialists in recent couple of decades. Various promising calculations have been produced towards the effective outline of such filters. These incorporate conventional methods like integer quadratic programming, optimization algorithms and so on. Contributory algorithms have been produced towards the decrease of adders in such channel circuits. Recently, this field has been appropriately enhanced with the incorporation of effective clever streamlining methods. This paper attempted to give a cutting edge concept by specific field. The above mentioned researchers focused on arithmetic complexity to reduce the area and power. The idea came into existence is that the memory design and the internal multiplier less operation gives the better operation in terms of area and power. The future work suggested here is to save the area and power by extending or improving the conventional methods. The inner product computation is to be carried out by the advanced optimization algorithms. Also it is suggested to implement the memory efficient FIR filter design to process some real time medical signal processing.

#### References

- Agarwal, M., Barsainya, R., &Rawat, T. K. (2016, April). Implementation of low power reconfigurable parametric equalizer with row bypassing multiplier on FPGA. In Computing, Communication and Automation (ICCCA), 2016 International Conference on (pp. 1352-1357). IEEE.

- [2] Deshmukh, R. M., &Keote, R. (2015, April). Design of polyphase FIR filter using bypass feed direct multiplier. In Communications and Signal Processing (ICCSP), 2015 International Conference on (pp. 1640-1643). IEEE.

- [3] Ifeachor, E. C., & Jervis, B. W. (2002). Digital signal processing: a practical approach. Pearson Education.

- [4] Mohanty, B. K., &Meher, P. K. (2013). A high-performance energy-efficient architecture for FIR adaptive filter based on new distributed arithmetic formulation of block LMS algorithm. IEEE transactions on signal processing, 61(4), 921-932.

- [5] Ababneh, J. I., &Bataineh, M. H. (2008). Linear phase FIR filter design using particle swarm optimization and genetic algorithms. Digital Signal Processing, 18(4), 657-668.

- [6] Kotha, S. R., Vij, S., &Sahoo, S. K. (2014, February). A study on strategies and Mutant factor in differential evolution algorithm for FIR filter design. In Signal Processing and Integrated Networks (SPIN), 2014 International Conference on (pp. 50-55). IEEE.

- Jiang, A., & Kwan, H. K. (2013). WLS design of sparse FIR digital filters. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(1), 125-135.

- [8] Jiang, A., Kwan, H. K., & Zhu, Y. (2012). Peak-error-constrained sparse FIR filter design using iterative SOCP. IEEE Transactions on Signal Processing, 60(8), 4035-4044.

- [9] Kar, R., Mandal, D., Mondal, S., &Ghoshal, S. P. (2012). Craziness based particle swarm

optimization algorithm for FIR band stop filter design. Swarm and evolutionary computation, 7, 58-64.

- [10] Zhao, H., Ye, W. B., & Yu, Y. J. (2013, May). Sparse FIR filter design based on genetic algorithm. In Circuits and Systems (ISCAS), 2013 IEEE International Symposium on (pp. 97-100). IEEE.

- [11] Jiang, A., Kwan, H. K., Tang, Y., & Zhu, Y. (2014, June). Efficient design of sparse FIR filters with optimized filter length. In Circuits and Systems (ISCAS), 2014 IEEE International Symposium on (pp. 966-969). IEEE.

- [12] Raj, P. J., &Vigneswaran, T. (2016, March). A paradigm of distributed arithmetic (DA) approaches for digital FIR filter. In Electrical, Electronics, and Optimization Techniques (ICEEOT), International Conference on (pp. 4668-4672). IEEE.

- [13] Pak, J. M., Ahn, C. K., Shmaliy, Y. S., Shi, P., & Lim, M. T. (2016). Switching extensible FIR filter bank for adaptive horizon state estimation with application. IEEE Transactions on Control Systems Technology, 24(3), 1052-1058.

- [14] Park, S. Y., &Meher, P. K. (2014). Efficient FPGA and ASIC realizations of a DA-based reconfigurable FIR digital filter. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(7), 511-515.

- [15] Zhao, S., Shmaliy, Y. S., Huang, B., & Liu, F. (2015). Minimum variance unbiased FIR filter for discrete time-variant systems. Automatica, 53, 355-361.

- [16] Chandra, A., Chattopadhyay, S., & Ghosh, B. (2014). Design and Implementation of SORIGA-optimized Powers-of-two FIR Filter on FPGA. AASRI Procedia, 9, 51-56.

- Tseng, C. C., & Lee, S. L. (2014). Designs of fractional derivative constrained 1-D and 2-D FIR filters in the complex domain. Signal Processing, 95, 111-125.

- [18] Nagahara, M., & Yamamoto, Y. (2014). FIR Digital Filter Design by Sampled-Data\* H∞ Discretization. IFAC Proceedings Volumes, 47(3), 3110-3115.

- [19] Baderia, K., Kumar, A., & Singh, G. K. (2015). Hybrid method for designing digital FIR filters based on fractional derivative constraints. ISA transactions, 58, 493-508.

- [20] Dwivedi, A. K., Ghosh, S., &Londhe, N. D. (2016). Low power FIR filter design using modified multi-objective artificial bee colony algorithm. Engineering Applications of Artificial Intelligence, 55, 58-69.

- [21] Saha, S. K., Ghoshal, S. P., Kar, R., &Mandal, D. (2013). Cat swarm optimization algorithm for optimal linear

phase FIR filter design. ISA transactions, 52(6), 781-794.

- [22] Mandal, D., Kar, R., &Ghoshal, S. P. (2014). Digital FIR filter design using fitness based hybrid adaptive differential evolution with particle swarm optimization. Natural Computing, 13(1), 55-64.

- [23] Zhang, M., & Kwan, H. K. (2017, April). FIR filter design using multiobjective teaching-learning-based optimization. In Electrical and Computer Engineering (CCECE), 2017 IEEE 30th Canadian Conference on (pp. 1-4). IEEE.

- [24] Rani, S., & Sidhu, D. S. (2015). Design of Digital Band Stop FIR Filter using Craziness Based Particle Swarm Optimization (CRPSO) Technique.

- [25] Dash, J., Dam, B., & Swain, R. (2017). Optimal design of linear phase multi-band stop filters using improved cuckoo search particle swarm optimization. Applied Soft Computing, 52, 435-445.

- [26] Shao, P., Wu, Z., Zhou, X., & Tran, D. C. (2017). FIR digital filter design using improved particle swarm optimization based on refraction principle. Soft Computing, 21(10), 2631-2642.

- [27] Pak, J. M., Kim, P. S., You, S. H., Lee, S. S., & Song, M. K. (2017). Extended least square unbiased FIR filter for target tracking using the constant velocity motion model. International Journal of Control, Automation and Systems, 15(2), 947-951.

- [28] Dash, J., Dam, B., & Swain, R. (2017). Design of multipurpose digital FIR doubleband filter using hybrid firefly differential evolution algorithm. Applied Soft Computing.

- [29] Aggarwal, A., Rawat, T. K., &Upadhyay, D. K. (2016). Design of optimal digital FIR filters using evolutionary and swarm optimization techniques. AEU-International Journal of Electronics and Communications, 70(4), 373-385.

- [30] Kuyu, Y. C., &Vatansever, F. (2016). A new intelligent decision making system combining classical methods, evolutionary algorithms and statistical techniques for optimal digital FIR filter design and their performance evaluation. AEU-International Journal of Electronics and Communications, 70(12), 1651-1666.

- [31] Mankar, P. J., Pund, A. M., Ambhore, K. P., &Anjankar, S. C. (2016). Design and Verification of Low Power DA-Adaptive Digital FIR Filter. Procedia Computer Science, 79, 367-373.

- [32] Chandra, A., &Chattopadhyay, S. (2016). Design of hardware efficient FIR filter: a

review of the state-of-the-art approaches. Engineering Science and Technology, an International Journal, 19(1), 212-226.

- [33] Illa, A., Haridas, N., & Elias, E. (2016). Design of multiplier-less FIR filters with simultaneously variable bandwidth and fractional delay. Engineering Science and Technology, an International Journal, 19(3), 1160-1165.

- [34] Kaur, R., Patterh, M. S., &Dhillon, J. S. (2015). A new greedy search method for the design of digital IIR filter. Journal of King Saud University-Computer and Information Sciences, 27(3), 278-287.

- [35] Tsao, Y. C., & Choi, K. (2012). Areaefficient VLSI implementation for parallel linear-phase FIR digital filters of odd length based on fast FIR algorithm. IEEE Transactions on Circuits and Systems II: Express Briefs, 59(6), 371-375.

- [36] Tsao, Y. C., & Choi, K. (2011, May). Hardware-efficient parallel FIR digital filter structures for symmetric convolutions. In Circuits and Systems (ISCAS), 2011 IEEE International Symposium on (pp. 2301-2304). IEEE.

- [37] Tsao, Y. C., & Choi, K. (2012). Areaefficient parallel FIR digital filter structures for symmetric convolutions based on fast FIR algorithm. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20(2), 366-371.

- [38] Hatai, I., Chakrabarti, I., & Banerjee, S. (2015). An Efficient VLSI Architecture of a Reconfigurable Pulse-Shaping FIR Interpolation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(6), 1150-1154.

- [39] Reddy, K. S., &Sahoo, S. K. (2015). An approach for FIR filter coefficient optimization using differential evolution algorithm. AEU-International Journal of Electronics and Communications, 69(1), 101-108.

- [40] Mohanty, B. K., &Meher, P. K. (2016). A high-performance FIR filter architecture for fixed and reconfigurable applications. IEEE transactions on very large scale integration (VLSI) systems, 24(2), 444-452.

- [41] Swathi, G., &Revathy, M. (2014). Design of a Multi-Standard DUC Based FIR Filter Using VLSI Architecture. International Journal of Scientific Engineering and Research (IJSER).

- [42] Hatai, I., Chakrabarti, I., & Banerjee, S. (2015). An efficient constant multiplier architecture based on vertical-horizontal binary common sub-expression elimination algorithm for reconfigurable FIR filter

synthesis. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(4), 1071-1080.

- [43] GPunitha, P., & Ramesh, R. (2015). Review of Memory Efficient 2-D Finite Impulse Response (FIR) Filter Architecture. Middle-East Journal of Scientific Research, 23(5), 957-961.

- [44] Liu, Y., &Parhi, K. K. (2017). Linear-Phase Lattice FIR Digital Filter Architectures Using Stochastic Logic. Journal of Signal Processing Systems, 1-13.

- [45] Lee, S. J., Choi, J. W., Kim, S. W., & Park, J. (2011). A reconfigurable FIR filter architecture to trade off filter performance for dynamic power consumption. IEEE transactions on very large scale integration (VLSI) systems, 19(12), 2221-2228.

- [46] Saranya K, RamaniKannan, ErmanAzwanYahya and Kishore Bingi, (2017) "Design of FIR filter using novel pipelined bypass multiplier", IEEE 3rd International Symposium on Robotics and Manufacturing Automation (ROMA).

- [47] Rashidi, B., Rashidi, B., &Pourormazd, M.

(2011, April). Design and Implementation of Low Power Digital FIR Filter based on low power multipliers and adders on Xilinx FPGA. In *Electronics Computer Technology* (*ICECT*), 2011 3rd International Conference on (Vol. 2, pp. 18-22). IEEE.

- [48] Liang, J., & Kwan, H. K. (2017, April). FIR filter design using multiobjective Cuckoo Search Algorithm. In *Electrical and Computer Engineering (CCECE), 2017 IEEE 30th Canadian Conference on* (pp. 1-4). IEEE.

- [49] Raju, R., & Kwan, H. K. (2017, April). FIR filter design using Multiobjective Artificial Bee Colony algorithm. In *Electrical and Computer Engineering (CCECE), 2017 IEEE 30th Canadian Conference on* (pp. 1-4). IEEE.

- [50] Mohanty, B. K., Meher, P. K., Al-Maadeed, S., & Amira, A. (2014). Memory footprint reduction for power-efficient realization of 2-D finite impulse response filters. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 61(1), 120-133.

- [51] Ahmad, A. A. (2014, October). VLSI architectures for Givens Rotation based RLS lattice ladder FIR filter algorithms using circular buffer technique. In Advances in Electronics, Computers and Communications (ICAECC), 2014 International Conference on (pp. 1-6). IEEE.

- [52] Johansson, H., &Eghbali, A. (2012, August). A realization of FIR filters with simultaneously variable bandwidth and

fractional delay. In *Signal Processing Conference (EUSIPCO), 2012 Proceedings of the 20th European* (pp. 2178-2182). IEEE.

#### **Author Profile**

Mr. L.Mohana kannan, received his M.E degree in Applied Electronics from K.S.Rangasamy College of Technology, Tiruchengode, Anna University Coimbatore, India in the year 2010. He joined as a Assistant Professor the Department in of

Electronics and Communication Engineering at RVS Technical Campus, Coimbatore, India during May 2010. He has 8 years of teaching experience. He is currently doing PhD in Anna University Chennai. His research interest includes signal Processing and its applications.

Dr. D. Deepa received her PhD from Anna University, India in Information and Communication Engineering in 2013. She received her M.E degree in Communication Systems from Anna University

Chennai in 2007. Currently, Dr. D. Deepa is working as a professor in the Department of Electronics and Communication Engineering at Bannari Amman Institute of Technology, India. She has more than 16 years of teaching and research experience. She has published more than 50 research papers in various International journals and conferences. Her research interest includes Speech signal processing, Image processing, Wireless Communications and its applications.