### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade PERUNDURAI -638 057, TAMILNADU, INDIA.

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# COURSE TITLE: VLSI DESIGN AND IMPLEMENTATION WITH XILINX VIVADO

PREPARED BY : S. DIVYA,

**Assistance Professor/ECE**

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

### 1. Introduction to Chip Design and FPGA

### 1.1 Basics of Chip Design: ASIC vs. FPGA

- ASIC (Application-Specific Integrated Circuit):

- **Definition:** A custom-designed integrated circuit (IC) tailored for a specific application.

- o **Characteristics:** High performance, low power consumption, small size, but high development cost and long time-to-market.

- o **Design Flow:** Involves complex and expensive steps like mask design, fabrication, and testing.

### • FPGA (Field-Programmable Gate Array):

- **Definition:** A semiconductor device containing an array of programmable logic blocks (PLBs) that can be configured by the user to implement various digital circuits.

- Characteristics: Flexible, reconfigurable, faster time-to-market compared to ASICs, but generally lower performance and higher power consumption than ASICs.

- Design Flow: Involves designing and programming the FPGA using hardware description languages (HDLs) like Verilog or VHDL.

### 1.2 Applications of FPGA in Chip Design and Prototyping

- **Prototyping:** FPGAs are widely used for prototyping ASIC designs, allowing for rapid design iterations and early verification.

- **Custom Computing:** FPGAs can accelerate specific algorithms and applications like image/video processing, machine learning, and high-performance computing.

- Communication Systems: FPGAs are used in various communication systems, including 5G, Wi-Fi, and data centers, for tasks like signal processing and protocol implementation.

- **Industrial Automation:** FPGAs are used in industrial control systems, robotics, and other applications requiring real-time processing and control.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

### PERUNDURAI -638 057, TAMILNADU, INDIA.

### 1.3 Overview of the Xilinx Vivado Design Suite

• **Integrated Design Environment (IDE):** A comprehensive software suite for designing, simulating, and implementing FPGA-based systems.

### • Key Features:

- o **HDL Editor:** Supports Verilog and VHDL for designing digital circuits.

- o **Synthesis:** Translates HDL code into a gate-level netlist.

- o **Implementation:** Maps, places, and routes the design onto the target FPGA device.

- o **Simulation:** Enables functional and timing simulations to verify design correctness.

- Debugging: Provides tools for debugging and analyzing the implemented design.

### 1.4 Advantages of Using FPGAs for Hardware Design

- **Flexibility and Reconfigurability:** FPGAs can be reprogrammed to implement different functions, making them adaptable to changing requirements.

- **Faster Time-to-Market:** Compared to ASICs, FPGAs have a shorter development cycle due to their reconfigurable nature.

- **Lower Development Costs:** FPGA development typically involves lower upfront costs compared to ASIC development.

- **Reduced Risk:** FPGAs allow for early design verification and risk mitigation before committing to ASIC fabrication.

- **Rapid Prototyping:** FPGAs enable rapid prototyping of complex systems, allowing for quick experimentation and design iterations.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

### 2. Overview of Xilinx Vivado Design Suite

### 2.1 Installation and Setup

- **Download:** Download the Vivado Design Suite installer from the Xilinx website. You'll likely need a Xilinx account to access the download.

- **Installation:** Run the installer and follow the on-screen instructions. Choose the appropriate installation options based on your needs and available disk space.

- **License:** Obtain a license for the Vivado Design Suite. Xilinx offers various licensing options, including academic licenses and commercial licenses.

- **Setup:** After installation, set up the Vivado environment by configuring your preferred workspace and other settings.

### 2.2 Features of Vivado

#### HDL Editor:

- o Supports Verilog and VHDL for designing digital circuits.

- Provides syntax highlighting, code completion, and other features for efficient code development.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

### • Synthesis:

Translates HDL code into a gate-level netlist, optimizing for area, performance, and power consumption.

### • Implementation:

- o **Place and Route:** Places and routes the synthesized netlist onto the target FPGA device, considering timing constraints and resource utilization.

- **Physical Design:** Optimizes the physical layout of the design for performance and power.

#### • Simulation:

- **Functional Simulation:** Verifies the functional correctness of the design before implementation.

- **Timing Simulation:** Verifies the timing behavior of the design after place and route.

### Debugging:

o Provides tools for debugging and analyzing the implemented design, such as ILA (Integrated Logic Analyzer) cores and JTAG debugging.

#### • IP Integrator:

- o A graphical interface for designing and integrating IP cores into your system.

- o Allows for easy connection and configuration of IP blocks.

### 2.3 Understanding the Vivado Workflow

### 1. **Design Entry:**

- Create or import HDL code (Verilog or VHDL) to describe the desired functionality.

- Optionally, use the IP Integrator to create a block diagram and add pre-designed IP cores.

### 2. Synthesis:

- o Translate the HDL code into a gate-level netlist.

- o Optimize the netlist for area, performance, and power.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

### PERUNDURAI -638 057, TAMILNADU, INDIA.

### 3. Implementation:

- Place and Route: Map, place, and route the design onto the target FPGA device.

- Physical Design: Perform optimizations like clock tree synthesis and power optimization.

#### 4. Bitstream Generation:

o Generate a bitstream file that can be downloaded to the target FPGA device to configure it with the designed logic.

#### 5. Verification:

- Perform functional and timing simulations to verify the correctness of the design.

- o Debug and refine the design as needed.

### 2.4 Using Vivado IP Integrator for Design Acceleration

- **Pre-designed IP Cores:** Utilize a vast library of pre-designed IP cores (e.g., processors, memories, peripherals) provided by Xilinx.

- **Block Diagram Design:** Create a block diagram of your system using the IP Integrator.

- **Easy Integration:** Connect and configure IP cores graphically, simplifying the design process.

- **Improved Productivity:** Accelerates design development by reusing pre-verified and optimized IP blocks.

- **System-Level Design:** Enables system-level design and integration of complex subsystems.

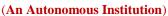

### Diagram: Vivado Design Flow

[Image of a diagram illustrating the Vivado design flow:

- 1. Design Entry (HDL code or IP Integrator)

- 2. Synthesis

- 3. Implementation (Place and Route)

- 4. Bitstream Generation

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

INNOVATION COUNCIL

PERUNDURAI -638 057, TAMILNADU, INDIA.

### 5. Verification (Simulation and Debugging)]

This diagram provides a visual representation of the typical design flow in the Vivado Design Suite. By understanding this flow and utilizing the powerful features of Vivado, you can efficiently design and implement complex FPGA-based systems.

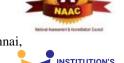

### 3. Basics of Verilog/VHDL for Chip Design

### 3.1 Overview of HDL Languages: Verilog and VHDL

Hardware Description Languages (HDLs) are specialized programming languages

used to describe the behavior and structure of digital circuits. They provide a textual

representation of the hardware, making it easier to design, simulate, and verify complex

circuits.

### • Verilog:

- o A widely used industry-standard HDL.

- Known for its concise syntax and C-like structure.

- o Popular for its readability and ease of use.

### • VHDL (VHSIC Hardware Description Language):

- o Another popular industry-standard HDL.

- More formal and structured compared to Verilog.

- Often preferred for large and complex designs due to its strong typing and design-for-testability features.

### 3.2 Writing Basic Combinational and Sequential Logic

### Combinational Logic:

- Output depends solely on the current input values.

- o Examples:

- **AND gate:** assign output = input1 & input2; (Verilog)

- **OR gate:** assign output = input1 | input2; (Verilog)

- MUX (multiplexer): Selects one of multiple inputs based on a control signal.

### • Sequential Logic:

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

- o Output depends on both current inputs and the past history of inputs (memory).

- Examples:

- Flip-Flop (D-Flip-Flop): Stores a single bit of data.

- always @(posedge clk) begin

- $q \le d$ ;

- end (Verilog)

- **Register:** An array of flip-flops used to store multiple bits of data.

- **Counter:** A sequential circuit that increments or decrements a value periodically.

### 3.3 Simulation and Testbench Creation in Vivado

• **Testbench:** A separate piece of HDL code that provides test stimuli (inputs) to the design under test (DUT) and observes the outputs.

#### • Creating a Testbench:

- o Define input signals and apply appropriate stimuli (e.g., clock signals, data patterns).

- o Monitor the outputs of the DUT and compare them with expected values.

#### • Simulation in Vivado:

- Use the Vivado simulator to execute the testbench and observe the behavior of the DUT.

- Analyze simulation waveforms to identify any design errors or unexpected behavior.

### 3.4 Debugging and Waveform Analysis

- **Waveform Viewer:** Vivado provides a waveform viewer to visualize the signals in the simulation.

- Debugging Techniques:

- o **Step-by-Step Simulation:** Execute the simulation step-by-step to observe the changes in signal values at each clock cycle.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

- Adding Probes: Monitor specific signals within the design to track their values during simulation.

- Using Assertions: Define assertions within the HDL code to check for specific conditions and detect design errors.

This diagram visually represents a simple example of a Verilog/VHDL module and its expected waveform behavior.

By understanding these fundamental concepts of Verilog/VHDL, you can effectively design, simulate, and implement digital circuits using the Xilinx Vivado design suite.

### 4. Design Flow for Chip Design Using Vivado

The Vivado design flow encompasses a series of steps to translate your design from high-level concepts to a bitstream file that can be loaded onto the target FPGA. Here's a breakdown of the key stages:

### 1. RTL Design and Behavioral Simulation

- **RTL Design:** This is the core of the design process. You write the hardware description (using Verilog or VHDL) to describe the functionality of your circuit. This includes defining modules, instantiating components, and specifying their behavior.

- **Behavioral Simulation:** Before proceeding to synthesis, it's crucial to perform behavioral simulation. This verifies the functional correctness of your RTL design by simulating it with a testbench that provides inputs and checks the expected outputs. This helps identify and correct any design errors early in the process.

### 2. Design Constraints and Synthesis Optimization

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

### • Design Constraints (XDC):

- o These are specifications that guide the synthesis and implementation tools.

- They include timing constraints (e.g., clock frequencies, input/output delays), area constraints, and placement constraints.

- Well-defined constraints are crucial for meeting timing requirements and optimizing resource utilization.

### • Synthesis:

- The synthesis tool translates the RTL code into a gate-level netlist, representing the design as a collection of logic gates.

- o During synthesis, you can apply optimization directives to guide the synthesis process and improve area, performance, and power consumption.

### 3. Floorplanning and Placement

- **Floorplanning:** This stage involves defining the high-level placement of major design blocks (e.g., processors, memories, peripherals) on the FPGA fabric. This can significantly impact performance and routing congestion.

- **Placement:** The placement tool determines the exact location of each logic element (e.g., LUTs, flip-flops) within the FPGA fabric based on the floorplanning and design constraints.

### 4. Timing Analysis and Power Estimation

#### • Timing Analysis:

- After placement and routing, the tool performs static timing analysis (STA) to check if the design meets the timing constraints (e.g., clock frequency, setup/hold times).

- o If timing violations are detected, you need to revise the design, adjust constraints, or make modifications to improve timing performance.

#### • Power Estimation:

- The tool estimates the power consumption of the design based on the placement and routing information.

- o This helps in optimizing the design for low power consumption.

Diagram: Vivado Design Flow

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

[Image of a diagram illustrating the Vivado design flow:

- 1. RTL Design and Behavioral Simulation

- 2. Design Constraints and Synthesis

- 3. Floorplanning and Placement

- 4. Timing Analysis and Power Estimation

- 5. Bitstream Generation]

This diagram visually represents the key stages in the Vivado design flow, highlighting the iterative nature of the process and the importance of thorough verification and optimization at each step.

By following this design flow and utilizing the powerful features of the Vivado design suite, you can successfully implement complex FPGA-based systems that meet performance, power, and area requirements.

### 5. Data Collection and Analysis Using Vivado

### 5.1 Generating Simulation Data from Vivado

- **Simulation Results:** During functional and timing simulations in Vivado, the simulator generates waveform files (e.g., VCD, FSDB) that capture the values of signals over time.

- Accessing Simulation Data: These waveform files can be accessed and analyzed within the Vivado environment using the waveform viewer.

### **5.2 Exporting Timing and Resource Utilization Reports**

- **Timing Reports:** Vivado generates comprehensive timing reports after place and route. These reports provide detailed information about:

- Critical Paths: The slowest paths in the design that determine the maximum operating frequency.

- o **Setup/Hold Times:** Analysis of setup and hold time margins for all flip-flops.

- Slack Values: The amount of time by which the timing constraints are met or violated.

- **Resource Utilization Reports:** These reports provide information about the utilization of FPGA resources, such as:

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

- o Number of LUTs (Look-Up Tables) used.

- Number of flip-flops used.

- DSP blocks used.

- Memory blocks used.

### 5.3 Parsing Vivado Output Files for Data Analysis

- **Report Files:** Vivado generates various report files in text format (e.g., timing reports, utilization reports, synthesis reports).

- **Data Extraction:** Python scripts can be used to parse these text files and extract relevant data, such as:

- Critical path delays

- Slack values

- Resource utilization statistics

- Power consumption estimates

### 5.4 Basics of Python for Data Processing

- **Libraries:** Python provides powerful libraries for data processing and analysis:

- o **Pandas:** For data manipulation and analysis, including data cleaning, transformation, and aggregation.

- NumPy: For numerical computing, including array operations and mathematical functions.

- **Matplotlib:** For creating visualizations (plots, charts) to analyze the extracted data.

### • Data Extraction with Python:

- Use Python's built-in functions (e.g., open(), readlines()) to read data from Vivado report files.

- Use string manipulation techniques to extract specific data points from the text.

- Use regular expressions to efficiently parse complex data formats.

#### Diagram: Data Collection and Analysis Workflow

### **ENGINEERING COLLEGE**

#### (An Autonomous Institution)

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

INSTITUTION'S

INNOVATION

COUNCIL

(Ministry of HRD initiative)

[Image of a diagram illustrating the data collection and analysis workflow in Vivado:

- 1. Run simulations and generate waveform files.

- 2. Generate timing and resource utilization reports.

- 3. Use Python scripts to parse report files and extract data.

- 4. Analyze and visualize data using Python libraries (Pandas, NumPy, Matplotlib).]

By effectively collecting and analyzing data from Vivado, you can gain valuable insights into the performance, resource utilization, and power consumption of your FPGA designs, enabling you to make informed design decisions and optimize your designs for the target FPGA device.

### 6. Basics of Python and Matplotlib for Visualization

### 6.1 Installing Python and Required Libraries

- Install Python:

- Download and install the latest version of Python from the official website (https://www.python.org/).

- **Install Required Libraries:** Use pip, the package installer for Python, to install the necessary libraries:

- o Matplotlib: pip install matplotlib

- o **NumPy:** pip install numpy (for numerical computations)

- Pandas: (Optional) pip install pandas (for data manipulation and analysis)

#### 6.2 Introduction to Matplotlib for Data Visualization

• **Matplotlib:** A powerful and versatile Python library for creating static, animated, and interactive visualizations in various formats.

### • Key Features:

- Supports a wide range of plot types: line plots, bar charts, histograms, scatter plots, 3D plots, and more.

- Offers extensive customization options for plot appearance (colors, markers, labels, legends).

- o Provides tools for interactive exploration of data (zooming, panning).

### 6.3 Plotting Vivado Simulation and Synthesis Results

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

#### • Extract Data:

- Parse Vivado report files (e.g., timing reports, utilization reports) using Python scripts.

- Extract relevant data:

- Critical path delays

- Slack values

- Resource utilization (LUTs, flip-flops)

- Clock frequency

#### Create Plots:

- Line Plots: Visualize changes in critical path delays or clock frequency across different design iterations.

- o **Bar Charts:** Compare resource utilization (LUTs, flip-flops) between different design versions or across different FPGAs.

- **Scatter Plots:** Analyze the relationship between different design parameters (e.g., clock frequency vs. area).

### 6.4 Customizing Graphs: Labels, Legends, and Styles

- Labels: Add clear and informative labels to axes (x-axis, y-axis), titles, and legends.

- Legends: Create legends to distinguish between different data series in the plot.

- **Styles:** Customize the appearance of the plot:

- o Choose different line styles, colors, and markers.

- o Adjust font sizes, line widths, and marker sizes.

- Control gridlines and background colors.

### **Example Python Script (Simplified):**

Python

import matplotlib.pyplot as plt

# Sample data (replace with actual data from Vivado reports)

### **ENGINEERING COLLEGE**

PERUNDURAI -638 057, TAMILNADU, INDIA.

clock\_frequencies = [100, 150, 200, 250] # MHz

lut\_utilization = [5000, 6000, 7500, 9000]

# Create the plot

plt.plot(clock\_frequencies, lut\_utilization, marker='o', linestyle='-', color='blue')

# Add labels and title

plt.xlabel('Clock Frequency (MHz)')

plt.ylabel('LUT Utilization')

plt.title('Clock Frequency vs. LUT Utilization')

# Show the plot

plt.show()

By effectively utilizing Python and Matplotlib, you can visualize and analyze the results of your FPGA designs, gain valuable insights into their performance and resource utilization, and make informed design decisions.

### Diagram: Data Visualization Workflow in Vivado

[Image of a diagram illustrating the data visualization workflow in Vivado:

- 1. Run Vivado simulations and generate reports.

- 2. Extract data from reports using Python scripts.

- 3. Process and analyze data using Python libraries (e.g., Pandas, NumPy).

- 4. Create visualizations using Matplotlib (line plots, bar charts, etc.).

- 5. Customize plots with labels, legends, and styles.]

This diagram provides a visual representation of the data visualization process, starting from data extraction from Vivado reports to the creation of insightful visualizations using Python and Matplotlib.

### 7. Performance Metrics in Chip Design

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

### 7.1 Timing Metrics

- **Setup Time:** The minimum time interval between the arrival of the data signal on the input of a flip-flop and the rising edge of the clock signal.

- **Hold Time:** The minimum time interval that the data signal must be stable after the rising edge of the clock signal before it can change.

- **Slack:** The difference between the required time and the actual time for a signal to arrive or change.

- o **Positive Slack:** Indicates that the timing constraint is met.

- Negative Slack: Indicates a timing violation.

### 7.2 Resource Utilization

- **LUTs** (**Look-Up Tables**): Basic building blocks of the FPGA fabric used to implement logic functions.

- **FFs** (**Flip-Flops**): Storage elements used to store data.

- **BRAMs** (**Block RAMs**): On-chip memory blocks for storing large amounts of data.

- **DSP Slices:** Dedicated hardware blocks for performing arithmetic operations (e.g., multiplication, addition) efficiently.

### 7.3 Power Consumption Analysis

- Dynamic Power:

- o Switching activity: Power consumed when logic gates change state.

- o Leakage power: Power consumed when the device is in standby mode.

#### • Static Power:

Leakage power: Power consumed by the device even when it is not actively switching.

### Visualizing Design Metrics using Matplotlib

- Plot Timing Metrics:

- **Slack Distribution:** Plot a histogram of slack values to identify critical paths and potential timing violations.

### **ENGINEERING COLLEGE**

Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade PERUNDURAI -638 057, TAMILNADU, INDIA.

• Clock Frequency vs. Slack: Plot the relationship between clock frequency and the minimum slack in the design.

### • Plot Resource Utilization:

- o **Bar charts:** Visualize the utilization of different resources (LUTs, FFs, BRAMs) across different design versions or under different operating conditions.

- **Pie charts:** Show the percentage of resources utilized for different components of the design.

### • Plot Power Consumption:

- **Line plots:** Plot power consumption over time or under different operating conditions.

- **Bar charts:** Compare power consumption between different design versions or operating modes.

### **Example Python Script (Simplified):**

Python

import matplotlib.pyplot as plt

# Sample data (replace with actual data from Vivado reports)

clock\_frequencies = [100, 150, 200, 250] # MHz

lut\_utilization = [5000, 6000, 7500, 9000]

# Create the plot

plt.plot(clock frequencies, lut utilization, marker='o', linestyle='-', color='blue')

# Add labels and title

plt.xlabel('Clock Frequency (MHz)')

plt.ylabel('LUT Utilization')

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

plt.title('Clock Frequency vs. LUT Utilization')

# Show the plot

plt.show()

By visualizing these key performance metrics, you can gain a better understanding of your FPGA design's behavior, identify areas for improvement, and make informed design decisions to optimize performance, power consumption, and resource utilization.

### **Diagram: Visualizing Design Metrics**

[Image of a diagram illustrating various plots for visualizing design metrics:

- Slack distribution histogram

- Clock frequency vs. Slack

- Resource utilization bar chart

- Power consumption line plot]

This diagram provides a visual representation of the types of plots that can be created to analyze and visualize key performance metrics in FPGA design using Matplotlib.

#### 8. Advanced Features in Xilinx Vivado

### 8.1 Using Advanced IP Cores in Vivado

- **Xilinx IP Catalog:** Vivado provides access to a vast library of pre-designed and preverified IP cores. These cores cover a wide range of functionalities, including:

- o **Processors:** MicroBlaze, ARM processors

- o **Peripherals:** UART, SPI, I2C, GPIO, timers, ADCs, DACs

- o **Memory:** Block RAMs, DDR controllers

- o **Communication:** Ethernet, USB, PCIe

- Video and Image Processing: Video codecs, image filters

### • Benefits of Using IP Cores:

• **Reduced Design Time:** Significantly reduces development time by reusing predesigned and tested components.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

- Improved Performance: Leverage optimized and high-performance IP cores from Xilinx.

- o **Increased Reliability:** Utilize pre-verified IP cores to minimize design risks.

- o **Faster Time-to-Market:** Accelerate the design cycle by integrating pre-existing, well-characterized IP blocks.

### 8.2 Partial Reconfiguration for Dynamic Designs

- **Partial Reconfiguration:** Allows you to dynamically reconfigure portions of the FPGA fabric while the system is running.

- Applications:

- **Adaptable Systems:** Adapt the FPGA functionality to changing requirements or environmental conditions.

- o **Software-Defined Radio:** Reconfigure the FPGA to handle different communication standards.

- Dynamic Load Balancing: Redistribute processing tasks across different parts of the FPGA to optimize performance.

- **Vivado Support:** Vivado provides tools and features to support partial reconfiguration, enabling you to define and implement reconfigurable regions within your design.

### 8.3 Integrating Custom IP Blocks into Vivado Projects

- Creating Custom IP: You can create your own custom IP blocks in Verilog or VHDL.

- **Packaging IP:** Package your custom IP into an IP core that can be easily integrated into other projects.

- **IP Integrator:** Use the IP Integrator to add your custom IP core to your design, connect it to other components, and configure its parameters.

### 8.4 Hardware Debugging with Vivado Logic Analyzer

- **Vivado Logic Analyzer (ILA):** A powerful debugging tool that allows you to capture and analyze signals within the FPGA fabric.

- **Real-time Signal Monitoring:** Capture and display real-time signals from the FPGA.

- **Triggering and Filtering:** Trigger data capture based on specific events and filter signals to focus on areas of interest.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

INSTITUTION'S

INNOVATION

COUNCIL

(Ministry of HRD Initiative)

• **Debugging Complex Issues:** Identify and debug timing issues, data corruption, and other hardware-related problems.

#### **Diagram: Advanced Features in Vivado**

[Image of a diagram illustrating advanced features in Vivado:

- Using IP cores

- Partial reconfiguration

- Integrating custom IP blocks

- Hardware debugging with ILA]

This diagram visually represents the advanced features available in the Vivado design suite, enabling you to create more complex and sophisticated FPGA-based systems. By effectively utilizing these features, you can significantly enhance your design productivity and achieve higher levels of design complexity and performance.

### 9. Integration of Hardware and Software Systems

### 9.1 Designing with Xilinx Zynq SoCs

• **Zynq SoCs:** These devices integrate a powerful ARM processor core (or cores) with programmable logic (FPGA) on a single chip.

### • Key Advantages:

- **Enhanced Processing Power:** Leverage the processing capabilities of the ARM processor for complex tasks.

- **Flexibility:** Combine the flexibility of FPGA logic with the processing power of the processor.

- o **Reduced System Complexity:** Integrate multiple functionalities (processing, control, I/O) onto a single chip.

### • Applications:

- o **Industrial Automation:** Motor control, robotics, machine vision.

- Communication Systems: Base stations, routers, switches.

- Medical Devices: Image processing, patient monitoring.

- Aerospace and Defense: Radar systems, signal processing.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

INNOVATION COUNCIL

### 9.2 Hardware-Software Co-design using Vivado and SDK

- **Vivado:** Used for designing and implementing the FPGA logic (PL).

- **SDK** (**Software Development Kit**): Used for developing software applications for the Processing System (PS).

- Co-design Process:

- o **Hardware Design:** Design and implement the FPGA logic using Vivado.

- **Software Development:** Develop software applications (e.g., in C/C++) to run on the ARM processor.

- Hardware-Software Integration:

- Define interfaces between the PL and PS (e.g., AXI interfaces).

- Develop drivers and libraries to allow the software to interact with the hardware.

- Utilize the Xilinx SDK to debug and optimize the integrated system.

### 9.3 Interfacing Peripherals like GPIO, UART, and I2C

- **Peripherals:** Zynq SoCs include various peripherals for interfacing with external devices.

- **GPIO** (**General Purpose Input/Output**): Used for digital input/output signals.

- UART (Universal Asynchronous Receiver/Transmitter): Used for serial communication.

- I2C (Inter-Integrated Circuit): Used for communication with other devices on the I2C bus.

- Interfacing with Peripherals:

- o **Hardware:** Configure the FPGA logic to interface with the desired peripherals.

- Software: Develop software drivers to control the peripherals from the ARM processor.

- Example:

- Configure GPIO pins as inputs or outputs in the FPGA.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

INNOVATION COUNCIL PERUNDURAI -638 057, TAMILNADU, INDIA.

Write software to read/write data to/from the GPIO pins using the appropriate driver.

### Diagram: Hardware-Software Co-design with Zynq

[Image of a diagram illustrating the hardware-software co-design process with Zynq SoC:

- 1. Design FPGA logic in Vivado.

- 2. Develop software applications in SDK.

- 3. Integrate hardware and software using AXI interfaces.

- 4. Interface with peripherals (GPIO, UART, I2C).

- 5. Debug and optimize the system.]

This diagram provides a visual representation of the hardware-software co-design process using Zynq SoCs, highlighting the integration of FPGA logic with the ARM processor and the importance of effective hardware-software interaction.

### 10. Case Studies and Hands-On Projects

Here are a few case studies and hands-on projects that can help you gain practical experience with Xilinx Vivado:

### 10.1 Design and Implementation of a 4-bit ALU

**Objective:** Design and implement a 4-bit Arithmetic Logic Unit (ALU) that performs various operations (addition, subtraction, multiplication, etc.) on two 4-bit input operands.

#### **Steps:**

- **Design:** Write Verilog/VHDL code to implement the ALU's logic.

- Simulation: Create a testbench to verify the functionality of the ALU for different input combinations and operations.

- **Synthesis and Implementation:** Synthesize, place, and route the design onto a target FPGA.

- **Verification:** Analyze timing reports and resource utilization to evaluate the design's performance.

### 10.2 FFT Processor Design and Visualization of Performance Metrics

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

• **Objective:** Design and implement a Fast Fourier Transform (FFT) processor on an FPGA.

### • Steps:

- o **Algorithm Implementation:** Choose an appropriate FFT algorithm (e.g., Radix-2 FFT) and implement it in Verilog/VHDL.

- **Performance Optimization:** Optimize the design for throughput and resource utilization.

- **Simulation and Analysis:** Simulate the FFT processor with different input signals and analyze its performance (e.g., latency, throughput, accuracy).

- **Visualization:** Use Python and Matplotlib to visualize the input and output signals of the FFT processor.

### 10.3 Low-Power Design and Analysis

• **Objective:** Design and implement a low-power digital circuit (e.g., a filter, a state machine).

#### • Steps:

- o **Power Optimization Techniques:** Explore techniques like clock gating, power gating, and voltage scaling to reduce power consumption.

- o **Implementation and Analysis:** Implement the design in Vivado and analyze the power consumption using the power estimation tools.

- o **Compare Power Consumption:** Compare the power consumption of different design implementations and identify areas for improvement.

#### 10.4 Digital Filter Implementation and Validation

• **Objective:** Design and implement a digital filter (e.g., low-pass filter, high-pass filter) on an FPGA.

#### • Steps:

- **Filter Design:** Choose the appropriate filter type and order, and determine the filter coefficients.

- o **Implementation:** Implement the filter using Verilog/VHDL, utilizing efficient arithmetic units (e.g., multipliers, adders).

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

### PERUNDURAI -638 057, TAMILNADU, INDIA.

- **Simulation and Testing:** Test the filter with various input signals and analyze its frequency response using simulation tools.

- o **Validation:** Compare the filter's performance with the expected characteristics.

### **Diagram: Case Study Examples**

[Image of a diagram illustrating the four case study examples:

- 4-bit ALU

- FFT Processor

- Low-power design

- Digital filter]

These case studies provide a starting point for your hands-on FPGA design projects. By working on these projects, you will gain practical experience in applying the concepts and tools learned throughout this course and develop a strong foundation in FPGA design and implementation.

### 11. Data Visualization for Chip Design

### 11.1 Visualizing Timing and Power Metrics using Matplotlib

• **Matplotlib:** A powerful Python library for creating various static, animated, and interactive visualizations.

#### • Benefits of Visualization:

- o **Improved Understanding:** Gain deeper insights into complex design data (timing reports, power reports).

- **Efficient Analysis:** Identify trends, patterns, and outliers in the data more easily compared to raw numbers.

- o **Effective Communication:** Clearly communicate design performance and trade-offs to stakeholders.

### **Visualizing Timing Metrics:**

### • Plot Types:

• **Line Plots:** Track changes in critical path delays or clock frequency across different design iterations.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

- o **Scatter Plots:** Analyze the relationship between clock frequency and area or between slack and operating temperature.

- **Histograms:** Visualize the distribution of slack values to identify critical paths and potential timing violations.

### **Visualizing Power Metrics:**

### • Plot Types:

- **Line Plots:** Plot power consumption over time or under different operating conditions (e.g., clock frequency, voltage).

- o **Bar Charts:** Compare power consumption between different design versions or operating modes.

- **Heatmaps:** Visualize the power consumption of different parts of the design for more complex analysis.

### 11.2 Comparing Multiple Design Iterations for Optimization

### Visualization Techniques:

- Overlay Plots: Overlay line plots or bar charts from different design iterations on the same graph to compare performance metrics (timing, power, resource utilization).

- o **Small Multiples:** Create a grid of multiple charts, each representing a different design iteration, allowing for quick visual comparison.

#### 11.3 Creating Interactive Plots for Large Datasets

• **Libraries:** Consider using libraries like Plotly or Bokeh for creating interactive visualizations.

#### • Benefits:

- o **Zooming and Panning:** Explore specific regions of interest within the data.

- o **Tooltips:** View detailed information about data points on hover.

- Filtering: Focus on specific subsets of the data for targeted analysis.

### 11.4 Reporting Design Progress with Matplotlib Visualizations

• **Integration with Reports:** Include Matplotlib visualizations in design reports and presentations to effectively communicate progress, challenges, and design decisions.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade **PERUNDURAI -638 057, TAMILNADU, INDIA.**

• **Customization:** Customize plots with clear labels, titles, and legends for better readability and understanding.

### 12. Challenges and Future Trends in Chip Design

### 12.1 Power and Area Trade-offs in FPGA-Based Design

• **Challenge:** Achieving optimal performance while minimizing power consumption and area utilization is a critical challenge in FPGA design.

#### Trade-offs:

- o **Performance vs. Power:** Increasing clock frequency or utilizing more resources can improve performance but often increases power consumption.

- o **Area vs. Performance:** Optimizing for minimal area may lead to reduced performance.

#### Strategies:

- Clock Gating: Disabling clock signals to inactive parts of the design to reduce power consumption.

- **Voltage and Frequency Scaling:** Operating the FPGA at lower voltages and frequencies to reduce power consumption.

- o **Design Techniques:** Employing low-power design techniques, such as pipelining and clock gating.

- Tool-Level Optimizations: Utilizing power optimization features within the Vivado design suite.

### 12.2 Emerging Trends

#### • AI Accelerators:

- Hardware Acceleration: FPGAs are increasingly used to accelerate AI/ML workloads (e.g., deep learning inference).

- Specialized Architectures: Development of specialized hardware architectures (e.g., systolic arrays) for AI/ML algorithms.

### • HBM (High Bandwidth Memory):

High-bandwidth interface: Provides high-bandwidth memory access for dataintensive applications.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

o **Improved Performance:** Enables higher data throughput and reduced memory access latency.

#### • RISC-V Cores:

- o **Open-Source Architecture:** Provides flexibility and customization for processor cores within the FPGA.

- o **Integration with FPGA Logic:** Enables tight integration of custom processing logic with a flexible and open-source processor core.

### 12.3 Future of Chip Design with Xilinx Vivado

- **Enhanced Design Tools:** Continued advancements in Vivado with improved automation, faster runtimes, and more advanced design exploration capabilities.

- **Integration with Cloud Platforms:** Seamless integration with cloud-based design and simulation services for improved collaboration and accessibility.

- **AI/ML-driven Design:** Utilizing AI/ML techniques for automated design exploration, optimization, and verification.

- Advanced Packaging Technologies: Support for advanced packaging technologies (e.g., 3D integration) to enable higher density and performance.

### 13. Deliverables

### 13.1 HDL Code for FPGA Designs

- Well-documented Verilog/VHDL Code:

- o Include clear and concise comments within your code to explain the functionality of each module and the design decisions made.

- o Use meaningful variable names and proper indentation for better readability.

#### • Testbenches:

- o Develop comprehensive testbenches for each module and the entire design.

- o Include test vectors for various input combinations and expected outputs.

### 13.2 Python Scripts for Data Visualization

• Data Extraction Scripts:

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

- Python scripts to parse Vivado report files (e.g., timing reports, utilization reports, power reports).

- Extract relevant data: critical path delays, slack values, resource utilization (LUTs, FFs, BRAMs), power consumption.

### • Visualization Scripts:

- Matplotlib scripts to create various plots:

- Line plots: Track changes in clock frequency, power consumption, or performance metrics over design iterations.

- Bar charts: Compare resource utilization across different design versions or operating conditions.

- Histograms: Analyze the distribution of slack values.

- Scatter plots: Visualize relationships between different design parameters.

### 13.3 Final Project Report with Visualized Performance Metrics

### • Introduction:

- o Background and motivation for the project.

- o Project objectives and goals.

### Methodology:

- o Detailed description of the design process, including:

- Design architecture and implementation.

- Simulation and verification methodology.

- Synthesis and implementation steps.

- Description of the hardware and software tools used.

### Results and Analysis:

- Presentation of key results:

- Performance metrics (timing, area, power).

- Resource utilization statistics.

### **ENGINEERING COLLEGE**

Approved by AICTE, New Delhi, Permanently Affiliated to Anna University- Chennai, Accredited by National Board of Accreditation (NBA), New Delhi & National Assessment and Accreditation Council (NAAC), Bangalore with 'A' Grade

PERUNDURAI -638 057, TAMILNADU, INDIA.

- Simulation results and waveforms.

- **Visualization:** Include well-formatted and informative visualizations (created using Matplotlib) to illustrate the results:

- Plots of timing metrics (slack, clock frequency).

- Charts of resource utilization.

- Power consumption analysis.

### Discussion:

- o Discussion of challenges encountered and solutions implemented.

- o Analysis of design trade-offs and limitations.

- o Suggestions for future improvements and extensions.

### • Conclusion:

- Summary of key findings and conclusions.

- o Significance of the project and its potential applications.